眾所周知,傳統芯片制約了神經網絡的運算速度,同時功耗也較大,因此,越來越多全球領先的科研機構和企業開始積極地推進激發式類腦芯片的研發,進行不同的嘗試與探索。激發式類腦芯片,就是用電路模擬人腦神經網絡架構的芯片。目前針對激發式類腦芯片的信號完整性和電磁輻射研究還處于起步階段,很多極具挑戰性的難題尚待解決,包括擬腦尖峰信號環境下,激發式類腦芯片片上電磁信號傳輸機理、信號完整性和電磁輻射仿真建模問題以及優化設計方法等基礎性關鍵科學問題。信息學院李燕課題組針對這些關鍵問題,聚焦人工智能芯片中長期發展所面臨的挑戰,重點攻關人工智能激發式類腦芯片片上電磁完整性和電磁輻射的機理、建模、設計、優化等方面的關鍵技術。其關于人工智能芯片-類腦芯片信號完整性(Signal Integrity)領域取得的最新研究成果,發表到國際電路與系統領域頂級期刊IEEE Transactions on Circuits and Systems I:(T-CAS I)上。論文題目為“Modeling and Signal Integrity Analysis of RRAM-Based Neuromorphic Chip Crossbar Array Using Partial Equivalent Element Circuit (PEEC) Method”。

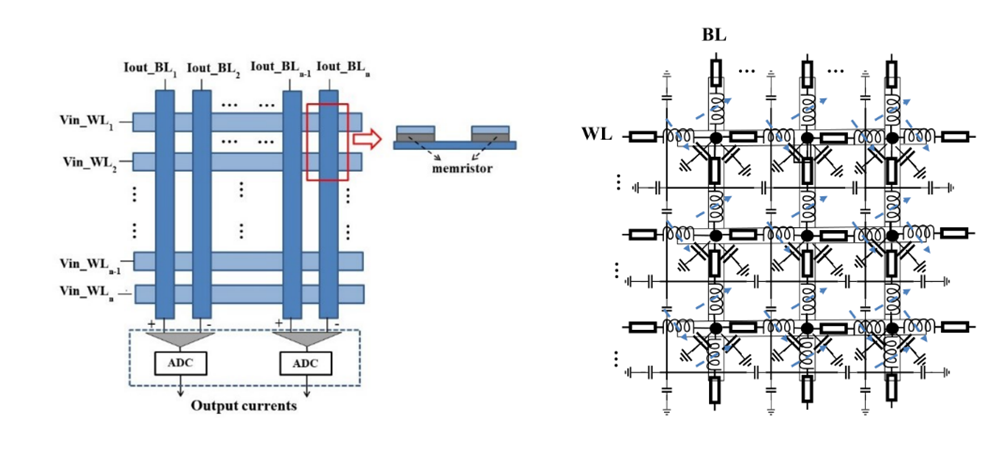

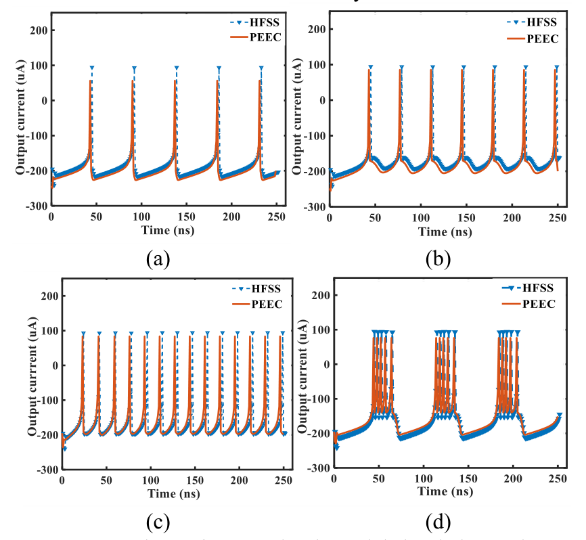

論文采用Izhikevich神經元模型產生的神經尖峰信號作為激勵源,全面研究了基于 RRAM 的類腦芯片交叉開關陣列中由互連寄生引起的信號完整性問題。通過部分等效元件電路(PEEC)方法計算獲得交叉開關陣列的寄生參數,對于 50×50 的陣列規模,該方法計算時間僅僅為商業軟件3D 模型1.5%,計算速度提高了 72 倍,有較高的計算效率。且PEEC 電路仿真結果與 3D 模型的結果非常吻合。團隊提出的簡單但有效的減少信號失真的設計方案,可為類腦神經形態系統實現高性能和高計算精度提供有價值的設計指導。

該研究工作獲國家自然科學基金面上項目、省自然基金重大項目等項目支持,與浙江大學射頻納米電子研究中心主任李爾平教授和新加坡A*STAR高性能計算研究院劉恩校教授合作。論文第一作者和通訊作者單位均為中國計量大學信息工程學院。《IEEE Transactions on Circuits and Systems I: Regular Papers》創刊于1952年,是IEEE電路與系統協會(IEEE Circuits and Systems Society)旗艦期刊,涵蓋所有集成電路與系統相關領域研究,屬于國際一流學術期刊。

信息學院李燕課題組具備良好的科研環境和資源,致力于培養學生的跨學科科研能力、實踐創新能力和領導力。鼓勵學生積極主動地探索前沿科學問題,關注國家攻堅難題,服務社會需要,成為工程俊杰。課題組還與華為有多項課題合作,解決重要工程問題。

[1] Y. Li et al., "Modeling and Signal Integrity Analysis of RRAM-Based Neuromorphic Chip Crossbar Array Using Partial Equivalent Element Circuit (PEEC) Method," in IEEE Transactions on Circuits and Systems I: Regular Papers, 2022, doi: 10.1109/TCSI.2022.3180199.